Process data

Data flow

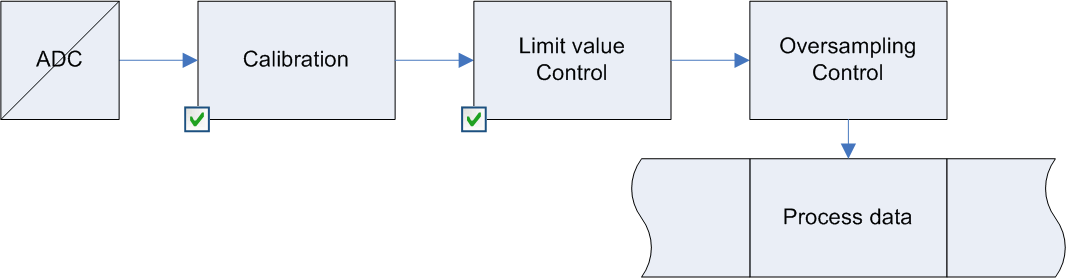

The amplitude values are measured with 16-bit resolution and provided as oversampling packets in the process image for cyclic transmission.

Fig.175: Process data flow EL3783

Fig.175: Process data flow EL3783Data processing

The data processing is done simultaneously for all channels in the EL3783 with 16-bit conversion in the ADC.

Scaling related to the respective (constant) measuring range:

Output value presentation

Voltage

EL3783 MBE: 737.2575 V (corresponds to approx. 130% * 400V * root(2) ) --> 22.5 mV / digit

EL3783-0100 MBE: 188.416 V (corresponds to approx. 130% * 100V * root(2) ) --> 5.75 mV / digit

Current

5 A range: MBE = 9,207527 (corresponds to approx. 130% * 5A * root(2)) --> 281µA / digit

1 A range: MBE = 1,8415054 (corresponds to approx. 130% * 1A * root(2)) --> 56,2µA / digit

3. Limit value evaluation (0x80p0:13, 0x80p0:14)

Display in the status word of the channel

If the value exceeds or falls below these values, which can be entered in the indices 0x80p0:13 and 0x80p0:14, then the bits in the indices 0x60p0:03 and 0x60p0:05 are set accordingly (see example below).

The entry 0x80p0:07 serves to activate the limit value monitoring.

Output limit n (2-bit):

- 0: not active

- 1: One or more values <= Limit n

- 2: One or more values >= Limit n

- 3: Cases 1 and 2 simultaneously

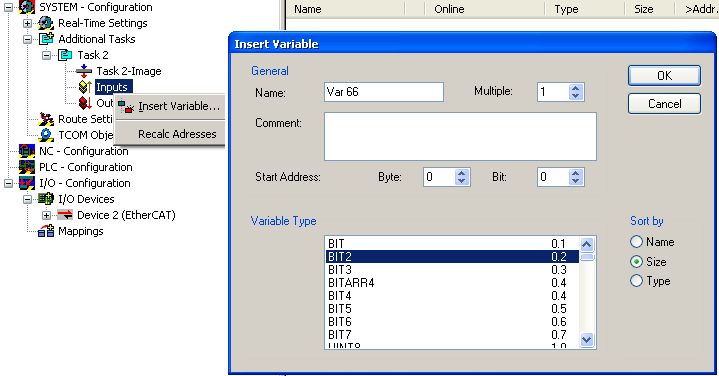

| Linking in the PLC with 2-bit values The limit information consists of 2 bits. Limitn can be linked to the PLC or a task in the System Manager:

|

Fig.176: Linking of 2-bit variable to additional task

Fig.176: Linking of 2-bit variable to additional taskExample of voltage measurement with EL3783:

Channel 1; Limit 1 and Limit 2 enabled, Limit 1 = 100 V, Limit 2 = 200 V, representation: signed integer

Entry in index (Limit 1): 0x8000:13

100 V / (0,0225 V / digit) = 4444dec

Entry in index (Limit 2): 0x8000:14

200 V / (0,0225 V / digit) = 8889dec

Output:

Input channel 1 | Index 0x6000:03 | Index 0x6000:05 |

|---|---|---|

50 V | 0x01hex, (Limit 1, limit value undershot) | 0x01hex, (Limit 2, limit value undershot) |

100 V | 0x03hex, (Limit 1, limit value reached) | 0x01hex, (Limit 2, limit value undershot) |

150 V | 0x02hex, (Limit 1, limit value exceeded) | 0x01hex, (Limit 2, limit value undershot) |

210 V | 0x02hex, (Limit 1, limit value exceeded) | 0x02hex, (Limit 2, limit value exceeded) |

4. Provision in the process data

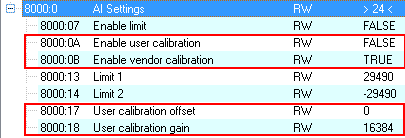

The influencing parameters can be changed in the CoE of the respective channel.

Fig.177: User settings and vendor calibration in the CoE online directory

Fig.177: User settings and vendor calibration in the CoE online directory | Changes in the CoE directory In case of changes to the CoE default parameters, it is essential that corresponding values are entered in the start-up list, so that in the case of exchange the EL3783 operates again as foreseen in the application. |

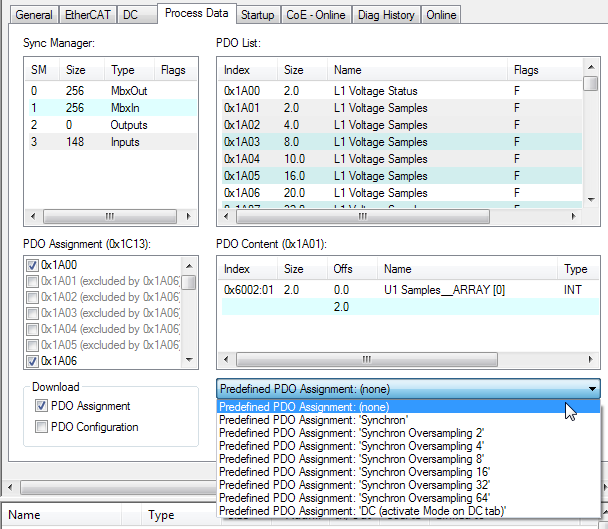

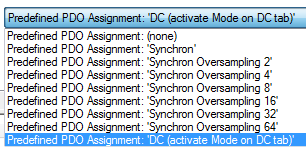

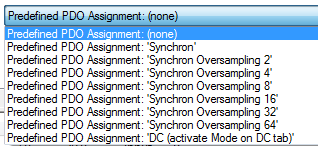

Predefined PDO Assignment

The "Predefined PDO Assignment" enables a simplified selection of the process data.

The desired function is selected on the lower part of the "Process Data" tab. As a result, all necessary PDOs are automatically activated and the unnecessary PDOs are deactivated.

8 PDO assignments are available:

Name | SM3, PDO assignment, meaning |

|---|---|

Synchronous | 0x1A00, 0x1A01, 0x1A10, 0x1A11, 0x1A20, 0x1A21, 0x1A30, 0x1A31, 0x1A40, 0x1A41, 0x1A50, 0x1A51 |

Synchronous oversampling 2 | 0x1A00, 0x1A02, 0x1A10, 0x1A12, 0x1A20, 0x1A22, 0x1A30, 0x1A32, 0x1A40, 0x1A42, 0x1A50, 0x1A52 |

Synchronous oversampling 4 | 0x1A00, 0x1A03, 0x1A10, 0x1A13, 0x1A20, 0x1A23, 0x1A30, 0x1A33, 0x1A40, 0x1A43, 0x1A50, 0x1A53 |

Synchronous oversampling 8 | 0x1A00, 0x1A05, 0x1A10, 0x1A15, 0x1A20, 0x1A25, 0x1A30, 0x1A35, 0x1A40, 0x1A45, 0x1A50, 0x1A55 |

Synchronous oversampling 16 | 0x1A00, 0x1A07, 0x1A10, 0x1A17, 0x1A20, 0x1A27, 0x1A30, 0x1A37, 0x1A40, 0x1A47, 0x1A50, 0x1A57 |

Synchronous oversampling 32 | 0x1A00, 0x1A0A, 0x1A10, 0x1A1A, 0x1A20, 0x1A2A, 0x1A30, 0x1A3A, 0x1A40, 0x1A4A, 0x1A50, 0x1A5A |

Synchronous oversampling 64 | 0x1A00, 0x1A0D, 0x1A10, 0x1A1D, 0x1A20, 0x1A2D, 0x1A30, 0x1A3D, 0x1A40, 0x1A4D, 0x1A50, 0x1A5D |

DC (activate Mode on DC tab) | 0x1A00, 0x1A05, 0x1A10, 0x1A15, 0x1A20, 0x1A25, 0x1A30, 0x1A35, 0x1A40, 0x1A45, 0x1A50, 0x1A55 |

Fig.30: EL3783 Selection dialog "Predefined PDO Assignment"

Fig.30: EL3783 Selection dialog "Predefined PDO Assignment"Process image

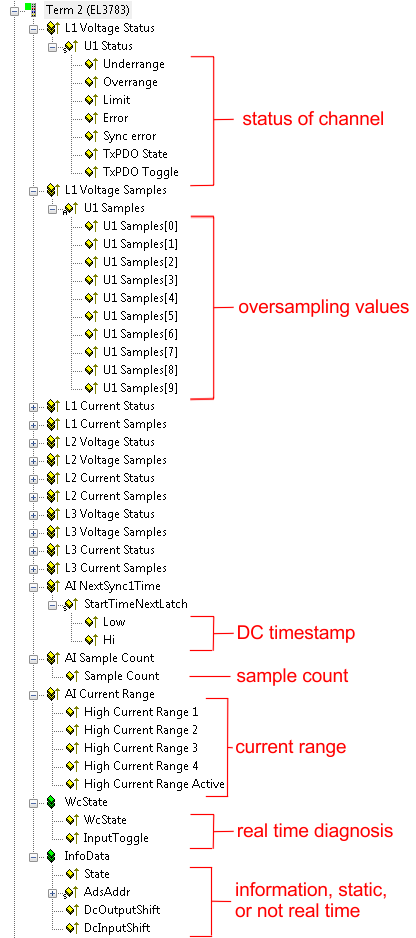

The EL3783 is inserted into the configuration by default with the 10-fold oversampling process image and DC timestamp:

Fig.179: Process image of the EL3783 in the TwinCAT System Manager

Fig.179: Process image of the EL3783 in the TwinCAT System ManagerIn particular the EL3783 offers the following cyclic information:

Variable | Meaning |

|---|---|

Status word | See below |

Overrange | Value after calibration > 0x7FFF |

Underrange | Value after calibration < 0x8000 |

SyncError | - In DC mode: indicates whether a synchronization error occurred in the expired cycle. |

StartTimeNextLatch (LO/HI) | In the 64-bit-wide process data StartTimeNextLatch, as was also the case with previous EL37xx terminals, the time is specified in each process data cycle when the next SYNC1 pulse and thus the next block of sample values begins, referenced to the currently transmitted block. StartTimeNextLatch thus changes in each cycle by the amount of that task cycle time with which this terminal is operated. This time specification is based on the terminal’s local Distributed Clocks time. Example: |

Sample Counter | The Sample Counter is incremented by one unit with each process data cycle. The Sample Counter enables the higher-level controller to check whether a data record has possibly been omitted or transmitted twice. In that case the DC shift time of the terminal usually has to be adapted. |

Current range | High Current Range 1-4 give information about the current range of each sample. High Current Range Active describes cycle by cycle whether the 5A range was switched on or not. |

DcOutputShift, DcInputShift | In these static variables the System Manager announces the shift time to which this terminal has been set. The value is set once on activating/calculating the configuration and also depends on the customer-specific settings in the extended slave settings. |

| Evaluation of the diagnostic values It is urgently recommended to evaluate the offered diagnostic values in the controller, e.g. see the notes page. |

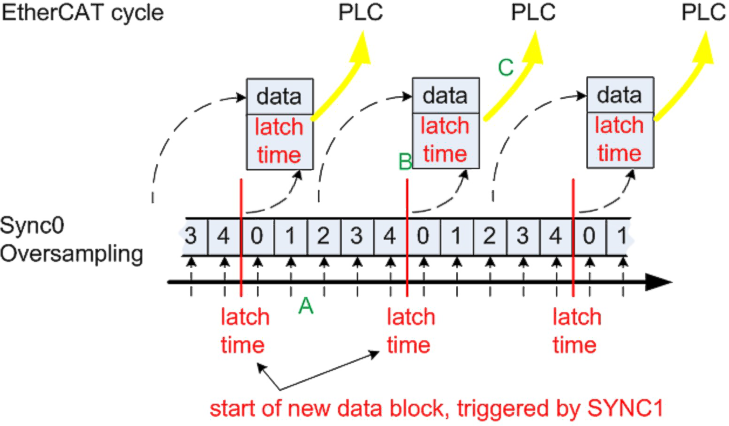

Correlation between timestamp and process data

The figure "Timing relationship between SYNC signals and SyncManager interrupt" illustrates the function and the timing relationship between time stamp and measured values.

For explanation::

- shown is an example for oversampling factor = 5

- the SYNC0 signal in the terminal triggers the AD conversion and fills the internal buffer with 5 measured values (A)

- SYNC1 runs synchronously with the cycle time, which triggers the supply of the filled buffer as process date and simultaneously fetches the StartTimeNextLatch from the local DistributedClock (B)

- the data block is assembled together with the next LatchTime

- the next EtherCAT cycle fetches this data (C)

Fig.180: Timing relationship between SYNC signals and SyncManager interrupt

Fig.180: Timing relationship between SYNC signals and SyncManager interruptControl/status word

Status word

The status word (SW) is located in the input process image, and is transmitted from terminal to the controller.

Bit | SW.15 | SW.14 | SW.13 | SW.12 | SW.11 | SW.10 | SW.9 | SW.8 |

Name | TxPDO Toggle | TxPDO State | Sync error | - | - | - | - | - |

Bit | SW.7 | SW.6 | SW.5 | SW.4 | SW.3 | SW.2 | SW.1 | SW.0 |

Name | - | ERROR | - | - | Limit 1 | Overrange | Underrange | |

Bit | Name | Description | |

|---|---|---|---|

SW.15 | TxPDO Toggle | 1bin | Toggles with each new analog process value |

SW.14 | TxPDO State | 1bin | TRUE in the case of an internal error |

SW.13* | Sync error | 1bin | TRUE (DC mode): a synchronization error occurred in the expired cycle. |

SW.6 | ERROR | 1bin | General error bit, is also set together with overrange and underrange |

SW.3 | Limit 1 | 1bin | See Limit |

SW.2 | 1bin | ||

SW.1 | Overrange | 1bin | Analog input signal lies above the upper permissible threshold for this terminal |

SW.0 | Underrange | 1bin | Analog input signal lies under the lower permissible threshold for this terminal |

Control word

The EL3783 has no control word

Synchronization, trigger and conversion time

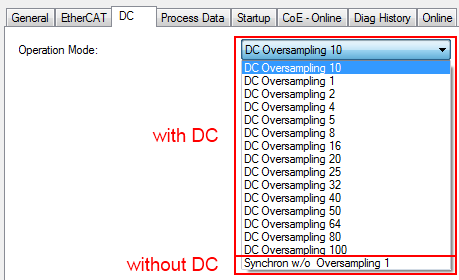

The EL3783 generally operates in oversampling mode. It can be operated with and without Distributed Clocks activated.

Distributed Clocks activated

- the EtherCAT system-wide synchronized Distributed Clocks also encompass this EL3783

- the terminal then operates synchronously with all other DC devices

- the sampling clock is derived from the local DC in the EtherCAT slave controller (SYNC0: Oversampling, SYNC1: Provision of the data)

Advantages

- several EL3783 record the measured values of all their channels synchronously

- accurate time stamp of the individual samples

Cycle times

The minimum EtherCAT cycle time for the EL3783 is 50 µs (see table in chapter “Quickstart”).

In order to activate Distributed Clocks, "DC" is to be selected in the Predefined PDO list, so that amongst others the time stamp PDO is selected

Fig.181: EL3783 Selection dialog "Predefined PDO Assignment"

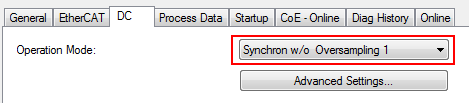

Fig.181: EL3783 Selection dialog "Predefined PDO Assignment" The permissible oversampling rates are set via the System Manager DC tab:

Fig.182: Setting of the oversampling rates via System Manager, "DC" tab

Fig.182: Setting of the oversampling rates via System Manager, "DC" tabDistributed Clocks not activated

- the EL3783 operates according to an internal clock, which is synchronized to the EtherCAT cycle time. The trigger point in this case is the access to the input Sync Manager SM3.

- As a result the EL3783 can compensate fluctuations in the cycle time to a large extent

- The EL3783 can thus be used in systems that have no Distributed Clocks functionality. The time accuracy of the measured values is reduced, however.

The EtherCAT cycle time must be selected such that

- it is not less than 200 µs (see table in chapter “Quickstart”)

- the oversampling interval does not produce a non-periodic time value – for example, 33.3 µs is not allowed for the oversampling cycle

The Distributed Clock is to be deactivated in the DC tab

Fig.183: Deactivation of the Distributed Clock in the "DC" tab

Fig.183: Deactivation of the Distributed Clock in the "DC" tabThe permissible oversampling rates are then set via the System Manager:

Fig.184: EL3783 Selection dialog "Predefined PDO Assignment"

Fig.184: EL3783 Selection dialog "Predefined PDO Assignment"