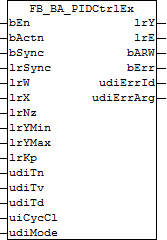

FB_BA_PIDCtrlEx

Universal PID controller, alternatively in parallel structure or with upstream proportional component

Functional description

This controller can be used either in parallel PID-structure or with a pre-positioned P-Part. The mode can be selected wit a proper entra at the input udiMode.

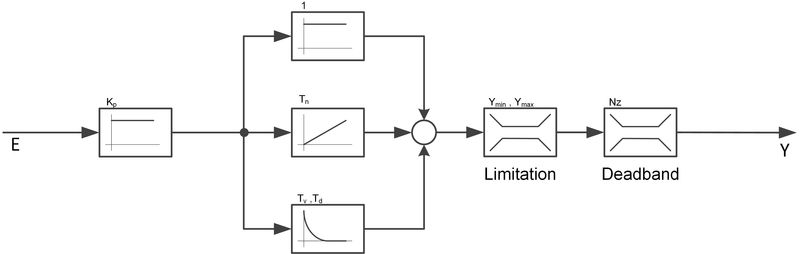

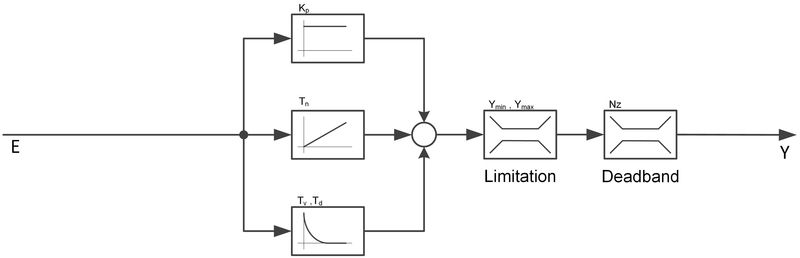

Functional diagram

udiMode=0 (P-part pre-positioned):

udiMode=1 (parallel-structure):

Passive behaviour (bEn = FALSE or bErr = TRUE)

The outputs are set as follows:

lrY | 0.0 |

lrE | 0.0 |

bAct | FALSE |

bARW | FALSE |

bMinLim | FALSE |

bMaxLim | FALSE |

bIncLim | FALSE |

bDecLim | FALSE |

In the event of an error, bErr is TRUE; udiErrId and udiErrArg describe the error. The internal values for the P-, I-, and D-components are set to 0, also the values for the I- and D-components of the preceding cycle. This ensures that the control value is "clean" in the first cycle after a restart, i.e. it is calculated without historical values.

Active behaviour (bEn = TRUE and bErr = FALSE)

In the first cycle, the I and D components are calculated "clean", i.e. without historical values, as already mentioned. A positive signal on bSync sets the I component so that the control value assumes the value lrSync. If bEn and bSync are set at the same time, this method can be used to set an initial value from which the controller "sets off". If the I component is not active, the D component is set accordingly. Note that only the rising edge of bSync is evaluated internally as this is a setting action. A TRUE signal must be applied again to the input bSync for renewed synchronization, for instance with a transfer value. If the I component is active, the controller ensures that it is retained, if the controller output lrY is at the limits lrYMin or lrYMax and about to fall or increase further. This procedure is referred to as Anti-Reset-Wind-Up. It ensures that the I component is always only just sufficiently large to enable the control value to assume values within the limit immediately after a control deviation, without having to deal with an integral component that has become too large.

Control direction

If bActn = FALSE, the control direction of the controller is reversed so that a control deviation of less than 0 causes a change in the control value in the positive direction. This is achieved by a negative calculation of the control deviation:

bActn | rXW (control deviation) | Control direction |

|---|---|---|

TRUE | lrX-lrW (actual value-set value) | direct (cooling) |

FALSE | lrW-lrX (set value-actual value) | indirect (heating) |

Anti-Reset-Windup when the maximum or minimum value is reached

If the controller reaches its upper limit at the output and the control deviation is still positive, the integral component will continue to increase, until the control deviation is less than or equal to zero again. This may lead to an unnecessarily large integral component, which would have to be reduced again, if the sign of the control deviation changes and would make the control behavior sluggish. The same applies if the minimum values is reached at the output, while the control deviation is still negative. To prevent this, the I component is not recalculated when one of these two cases occurs, but it is held at the value of the preceding PLC cycle. If a sign inversion occurs, i.e. if the maximum value is reached and the control deviation is less than 0.0 or the minimum value is reached and the control deviation is greater than 0.0, the I-component is calculated again.

Neutral zone (deadband)

A value of lrNZ > 0.0 enables the neutral zone function. If lrNZ is 0 the deadband-part is deactivated and the values at its input are put through.

If the deadband is activated, the value at the input will only be put through as a new ouput-value if the difference between input-value and current output-value is greater or equal to lrNZ/2.

Example: lrNZ = 1, lrYin = 55.0, lrYout= 55.0 (the input-value was just put through)

PLC-Cycle+1 | lrYin=55.2 | lrYout=55.0 |

PLC-Cycle+2 | lrYin=55.3 | lrYout=55.0 |

PLC-Cycle+3 | lrYin=55.1 | lrYout=55.0 |

PLC-Cycle+4 | lrYin=55.6 | lrYout=55.6 |

PLC-Cycle+5 | lrYin=55.4 | lrYout=55.6 |

PLC-Cycle+6 | lrYin=55.3 | lrYout=55.6 |

PLC-Cycle+7 | lrYin=55.1 | lrYout=55.1 |

This function is intended to avoid an unnecessarily large number of actuating pulses.

Autocorrection of parameters

For parameters it makes sense to correct or limit them automatically, without issuing an error message, since the user expectation is clear:

- lrSync > lrYMax -> lrSync := lrYMax

- lrSync < lrMin -> lrSync := lrMin

- uiCycCl = 0 -> uiCycCl := 1

Inputs/outputs

VAR_INPUT

bEn : BOOL;

bActn : BOOL;

bSync : BOOL;

lrSync : LREAL;

lrW : LREAL;

lrX : LREAL;

lrNZ : LREAL;

lrKp : LREAL;

udiTn : UDINT;

udiTv : UDINT;

udiTd : UDINT;

uiCycCl : UINT;

udiMode : UDINT;

bEn: controller activation

bActn: control direction of the controller

bSync / lrSync: synchronization command: set output value lrY to lrSync.

lrW: setpoint

lrX: actual value

lrNZ: neutral zone

lrYMin: lower controller output limit

lrYMax: upper limit of the working range of the controller

lrKp: controller amplification. Only affects the P component

udiTn: integral action time of the I component [ms]. A zero value at this parameter disables the I component.

udiTv: integral action time of the D component [ms]. A zero value at this parameter disables the D component.

udiTd: damping time of the D component [ms] .uiCycCl: call cycle of the function block as multiple of the cycle time. A zero entry is automatically interpreted as uiCycleCall =1.

Example: tTaskCycleTime = 20 ms, uiCtrlCycleCall =10 -> The control algorithm is called every 200 ms. Thus the outputs are also updated only every 200 ms.

udiMode: udiMode=0: controller with upstream P component, udiMode=1: controller in parallel structure.

VAR_OUTPUT

lrY : LREAL;

lrE : LREAL;

bARW : BOOL;

bErr : BOOL;

udiErrId : UDINT;

udiErrArg : UDINT;

lrY: control value. Range limited by lrYMin and lrYMax.

lrE: control deviation (calculation dependent on control direction)

bARW: Anti-Reset-Windup function is active.

bErr: this output is switched to TRUE if the parameters entered are erroneous.

udiErrId / udiErrArg: contains the error number and the error argument. See error codes.

Requirements

Development environment | Target system | required library | required supplement |

|---|---|---|---|

TwinCAT 2.11 R3/x64 | PC/CX | TcBA library from V1.0.0 | TS8040 | TwinCAT Building Automation from V1.0.0 |