Sampling of digital inputs

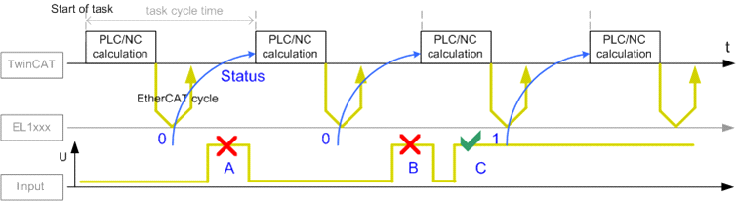

A PLC usually samples digital inputs once per PLC cycle. This type of sampling has two disadvantages:

- Short pulses that occur between the sampling times are not detected.

- The temporal resolution depends on the PLC cycle time.

Example

Pulses A and B are not detected in this figure. Only pulse C is long enough and present at the sampling time (blue arrow) so that the "1" is detected by the bus cycle.

Remedy

In order to compensate for the disadvantages mentioned, sampling methods have been developed that also enable precise temporal detection of very short pulses at any PLC cycle time:

- Oversampling

- Timestamp (EP1258-0001, EP1258-0002)

- Multi-timestamp (EP1258-0502)

Further Information