Oversampling

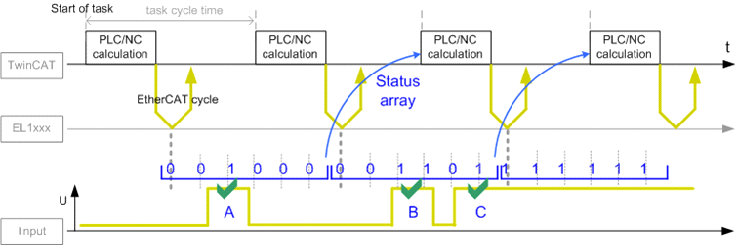

An oversampling input reads the state of the input n times within the specified (configurable) cycle time and saves the states in an array that is transferred to the controller in the bus cycle. The correspondingly finer time frame, the microcycle, thus enables a slow bus cycle time with nevertheless extremely fine sampling.

In this figure, pulses A and B are also detected in comparison to the standard sampling. Over the known microcycle time each individual pulse can be determined from the resulting data stream. However, a constantly high volume of data is transferred with each EtherCAT cycle, even if there are no edge changes at all at the input.