Principles of the oversampling function

The EL5101-0011 EtherCAT Terminal is an interface for direct connection of incremental encoders with differential inputs (RS422). Through the oversampling property the terminal can read the current counter value several times per bus cycle.

Oversampling

A conventional incremental encoder interface terminal reads a counter value with each bus cycle and passes it on to the higher-level controller in the next fieldbus cycle. The EL5101-0011 reads the current counter value at several configurable and equidistant times between two fieldbus communication cycles. The transfer of a packet of x position values of 32 bits each to the higher-level controller takes place in the next fieldbus communication cycle. This procedure is referred to as oversampling.

Distributed Clocks

Oversampling requires a clock generator in the terminal that triggers the individual data sampling events. The local clock in the terminal, referred to as distributed clock, is used for this purpose.

The distributed clock represents a local clock in the EtherCAT slave controller (ESC) with the following characteristics:

- Unit 1 ns

- Zero point 1.1.2000 00:00

- Size 64 bit (sufficient for the next 584 years); however, some EtherCAT slaves only offer 32-bit support, i.e. the variable overflows after approx. 4,2 seconds

- The EtherCAT master automatically synchronizes the local clock with the master clock in the EtherCAT bus with a precision of < 100 ns.

The EL5101-0011 offers 64-bit support.

Sample Oversampling with SYNC0 and SYNC1:

The fieldbus/EtherCAT master is operated with a cycle time (TSYNC1) of 1 ms to match the higher-level PLC cycle time of 1 ms, for example. This means that an EtherCAT frame is sent every 1 ms to the EL5101-0011 to collect the process data. Therefore, the local clock in the terminal triggers an interrupt every 1 ms (1 kHz) in the ESC (EtherCAT Slave Controller) that provides the process data promptly for the collecting EtherCAT frame. This first interrupt is called SYNC1.

The EL5101-0011 is set in the TwinCAT System Manager to an oversampling factor n = 100. This causes the ESC to generate a second interrupt in the terminal with an n-times higher frequency (FSYNC0), in this case 100 kHz or 10 µs period (TSYNC0). This interrupt is called SYNC0. The counter value is read on each SYNC0 signal; the values are stored in succession in a buffer. Generation of the SYNC0 pulse from the local synchronized clock within the distributed clock network ensures that the position values are sampled at highly equidistant intervals with the period of the SYNC1 pulse.

| Maximum sampling frequency / minimum cycle time A sampling time shorter than (TSYNC0) 10 µs is not permissible for the EL5101-0011! |

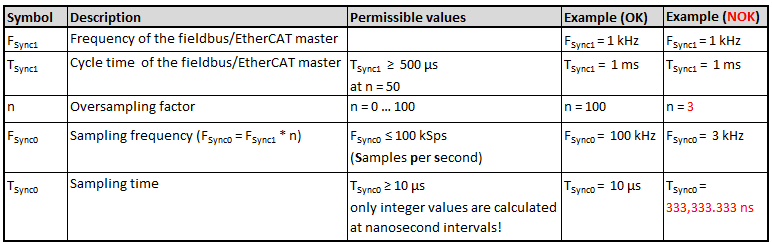

Sample permissible and impermissible oversampling factors:

For TSYNC1 = 1 ms oversampling factors such as 1, 2, 5 or 100 are permitted, but not 3! If implausible values are use the terminal will reach the OP state but will not supply any process data.

This may result in a working counter error.

The 32-bit measured values accumulated in the buffer are sent as a packet to the higher-level control system.

Summary:

Time-related cooperation with other terminals

The reading of the measured values in the EL5101-0011 is triggered by an interrupt generated by the local clock in the terminal. All local clocks in the supporting EtherCAT slaves are synchronized. This enables EtherCAT slaves (here: terminals) to sample measured values simultaneously (simultaneous interrupt generation), independent of the distance between them. This simultaneity is within the distributed clock precision range of < 100 ns.

Sample for Coordination of two EL5101-0011 terminals with each other:

The EtherCAT master, e.g. Beckhoff TwinCAT, configures both EL5101-0011 terminals such that their SYNC1 pulses occur at the same time.

Assumption: The EtherCAT bus cycle time is 500 µs. The SYNC1 is thus triggered in all EL5101-0011 terminals every 500 µs.

- If both terminals operate with a corresponding oversampling factor (e.g. n = 20), the SYNC0 pulse correlating to SYNC1 will occur simultaneously in all EL5101-0011, in this sample TSYNC0 = 25 µs.

- If different oversampling factors are used in the EL5101-0011 terminals employed, their SYNC0 pulses no longer occur simultaneously. The higher-level SYNC1 pulse is retained.

Timestamp of the process data

The EL5101-0011 offers a "timestamp" for each process data block. This process data is already activated as StartTimeNextLatch through the activation of 0x1A01 ENC NextSync1Time as a 64-bit value in default on the Process data tab (see chapter Process data).

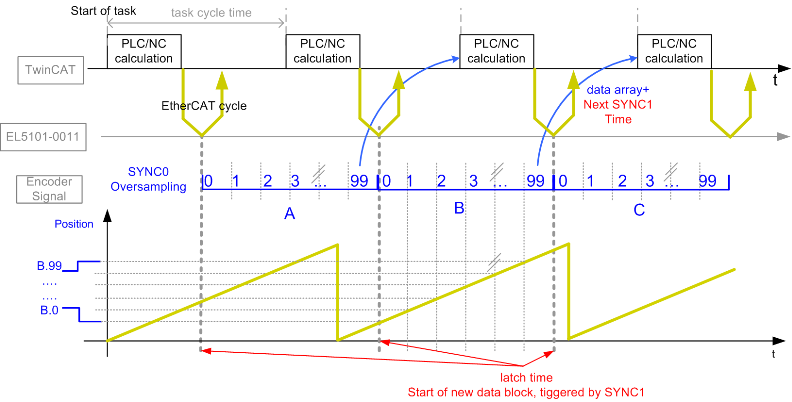

The data block consisting of sample value + timestamp, which is transferred in each cycle, is not related. The relationship is shown in the figure below.

To explain in more detail:

- The sample is based on an oversampling factor n = 100.

- The SYNC0 signal in the terminal fills the internal buffer with 100 position values.

- SYNC1, which triggers the filled buffer to be made available as process data and at the same time fetches the StartTimeNextLatch from the local distributed clock, runs synchronous with the cycle time.

- The data array is thereby assembled together with the next SYNC1 Time.

- The next EtherCAT cycle fetches this data.

Fig.176: Temporal relationship between SYNC signals and SyncManager interrupt

Fig.176: Temporal relationship between SYNC signals and SyncManager interrupt