Features CoE

Depending on the main PDO/optional PDOs further settings can be selected in the CoE list (CAN over EtherCAT).

| Parameterization via the CoE list (CAN over EtherCAT) Please note the following general CoE information when using/manipulating the CoE parameters: - Keep a startup list if components have to be replaced - Differentiation between online/offline dictionary, existence of current XML description - Use “CoE reload” for resetting changes |

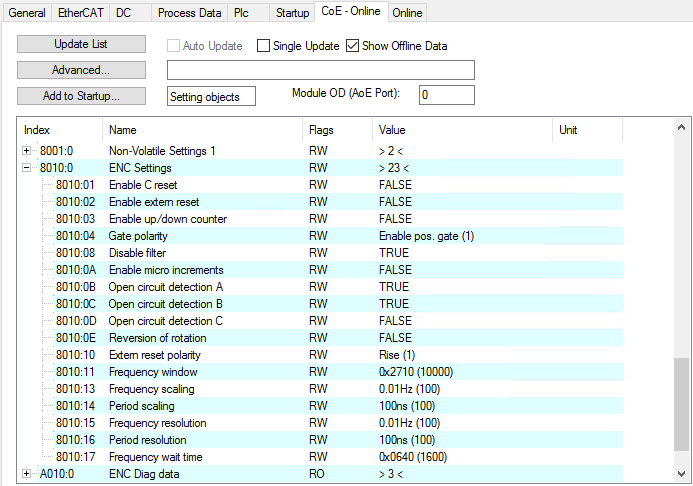

The following CoE settings are possible from object 0x8000 and are shown below in their default settings:

Fig.167: “CoE-Online” tab

Fig.167: “CoE-Online” tabThe parameters are described on page object description and parameterization.

Frequency

- The time window for the frequency calculation and the resolution can be parameterized in CoE objects 0x8000:11, 0x8000:13, 0x8000:15, 0x8000:17.

- The positive edges of track A are counted within the specified timeframe and the next edge including the time up to it are counted. The waiting time can be set in CoE object 0x8000:17 “Frequency Wait Time” (unit: ms). The default value is 1.6 sec. This is also the maximum value.

- The time window is 10 ms (default), min. 1 µs. With the default setting it is possible to measure frequencies up to approx. 800 kHz. At higher frequencies a smaller value must be selected for the timeframe.

- The time is measured with a resolution of 100 ns.

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- No frequency measurement is possible if the counter is blocked by the gate. In this case the period can be measured regardless.

- A C or external reset restarts the frequency measurement. The last frequency value remains unchanged until a new frequency value is determined.

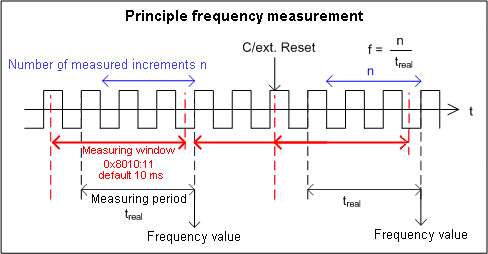

Frequency measurement

- Basic unit 1 µs: all window sizes

Measurement sequence

- The measurement starts with a positive edge at track A. The current counter value and time (resolution: 100 ns) are stored.

- After the measuring window time has elapsed (index 0x8000:11), the system waits for the following rising edge at track A or a maximum of 1.6 sec or the time from 0x8000:17

- The frequency is calculated from the edge difference and the actual elapsed time.

Fig.168: Frequency measurement principle in enhanced operation mode

Fig.168: Frequency measurement principle in enhanced operation modePeriod calculation

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- In each cycle the interval between two positive edges of input A is counted with a resolution of 100 ns.

- If no edge change occurs for approx. 1.6 s, any period specification is cancelled.

| Frequency and period measurement From the explanatory notes above it is apparent that the frequency measurement can measure the current axis status (velocity) significantly more accurately than the period measurement. Frequency measurement is therefore preferable, if possible. |

Latch

- Activation of latch C input (“C”) and saving (“latching”) of the counter value (index 0x7000:01)

- The counter value is saved at the first external latch pulse (positive edge at input “C”) after the bit has been set (TRUE) in index 0x7000:01 (has priority before 0x7000:02 / 0x7000:04). The subsequent pulses at the other inputs have no influence on the latch value in index 0x6000:12 if the bit is set.

- Note for “Latch C valid” bit: A new counter value at the latch input can only be written once the value of the “Latch C valid” bit (index 0x6000:01) is FALSE.

- Activation of the external latch input (“gate/latch”) and latching of the counter value (index 0x7000:02, 0x7000:04)

- The counter value at the latch input (Index 0x6000:12) will be saved upon the first external latch pulse with a rising edge if the bit (TRUE) is set in index 0x7000:02.The subsequent pulses have no influence on the latch value in index 0x6000:12.

- The counter value at the latch input (Index 0x6000:12) will be saved upon the first external latch pulse with a falling edge if the bit (TRUE) is set in index 0x7000:04. The subsequent pulses have no influence on the latch value in index 0x6000:12.

- Note for "Latch extern valid" bit: A new counter value at the latch input can only be written once the value of the “Latch extern valid” bit (index 0x6000:02) is FALSE.

Reset

- Counter reset (index 0x8000:01, 0x8000:02, 0x8000:10): For a counter reset via input C set the bit in index 0x80n0:01, for a reset via the external latch input set the bit in index 0x80n0:02.

- The functions “Enable C reset” (0x8000:01) and “Enable extern reset” (0x8000:02) cannot be activated simultaneously.

- Note for “Extern reset polarity”, index 0x8000:10: The edge for setting the counter to zero can be selected via index 0x8000:10.

Bit not set: counter is set to zero with falling edge.

Bit set: counter is set to zero with rising edge.

Open circuit detection

- A separate open circuit detection can be activated for each of the channels A, B and C (index 0x8000:0B, 0x8000:0C, 0x8000:0D).

- Open circuit detection is activated for channels A and B by default.

- A differential voltage of typically) and in the range of typically -0.475 V > Vid > +0.475 V is detected as an open ircuit.

- If an open circuit is detected, it is indicated as process data open circuit = TRUE. The bit in object 0x6000:07 is set. An open circuit is indicated separately in indices 0xA000:01 (track A), 0xA000:02 (track B) and 0xA0n0:03 (track C).

- TxPDO state also becomes TRUE if an open circuit is detected, since invalid data have to be assumed.