Hinweise

Hinweise zum Beispielprogramm des Slave-Systems

- Das Beispielprogramm zeigt das Slave-System (Systemumgebung B). Dieses erfordert eine Steuerung mit einer EtherCAT-Klemme EL1252. Sie können entweder einen Embedded PC verwenden, an dem die Klemme rechtsseitig angebracht wird, oder einen IPC mit einer EtherCAT-Verbindung eines z. B. RJ-45-Anschlusses zum EK1100-Koppler mit der Klemme. (Siehe auch Konfiguration)

- Lesen Sie die E/A‑Konfiguration gegebenenfalls neu ein und verknüpfen Sie die Variablen wie folgt:

- nIntTime → EL1252, PDO: Latch/ LatchPos1

- aEcMasterAmsNetId → Gerät (EtherCAT), PDO: InfoData/ AmsNetId

- bOut → (optional) EL2202-0100, PDO: Channel 1/ Output

- In dem Beispielprogramm wird nach Feststellung eines Ereignisses einer eingehenden positiven Flanke am Eingang der EL1252 der externe Zeitwert (nExtTime) entsprechend dem zu erwartenden Eingangssignal hochgezählt (50 ms Periodendauer → rEventTimeStep = 5·107). Wählen Sie je nach zu erwartender Periodendauer den entsprechenden Wert für rEventTimeStep:

nExtTime := nExtTime + LREAL_TO_ULINT(rEventTimeStep);

Die Addition eines konstanten Zeitwertes zu einem Basiszeitwert für den Zeitstempel der externen Zeit erfolgt in Abhängigkeit einer eingehenden (positiven) Flanke. Dadurch wird ein externer Zeitstempel durch den externen Takt abgebildet. Eine Flanke wird stets durch den Vergleich des aktuellen internen Zeitstempels, der von der EL1252 geliefert wird, mit dem jeweils letzten Zeitstempel in jedem Taskdurchlauf ermittelt:

IF(current_intTimeSatmp<>last_intTimeSatmp) THEN - Optional können Sie dem Projekt ein YT-Scope-View zur Veranschaulichung hinzufügen und

dabei folgende Variablen aus MAIN aufzeichnen: - nDcOffset (Ergebnis von FB_EcExtSyncIsSynchronized aus nExtTime und nIntTime)

- bExtTime_Digits und bIntTime_Digits zur Veranschaulichung des zeitlichen Drift bzw. Gleichlaufs nach Aktivierung des Synchronisierungsvorgangs

- bSynchronized zur Darstellung, dass die Synchronisation erfolgt ist

- Die Variable bEnableExtSync kann zu einen gewünschten Zeitpunkt auf TRUE gesetzt werden.

Allgemeine Hinweise zum Master-System

- Das Master-System ist in diesem Beispiel nicht enthalten. Als Master‑System kommen generell alle Zeitgeber in Betracht, die ein 24-V‑Rechtecksignal bereitstellen können. Das im Aufbau dargestellte Master‑System hat Distributed‑Clocks (DC) seitens der EtherCAT-Klemme EL2202‑0100 aktiviert und für ein Ausgangssignal mit T = 50 ms eine entsprechende Taskzykluszeit von 25 ms eingestellt. Für das Erzeugen des Ausgangssignals dient die folgende Codezeile in der (POU) MAIN:

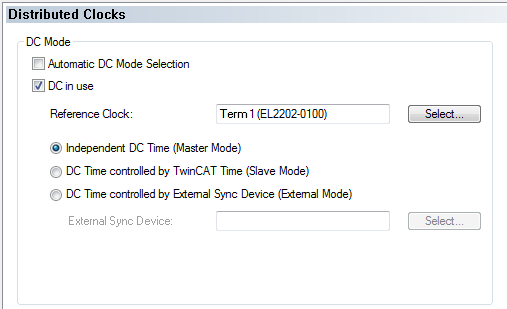

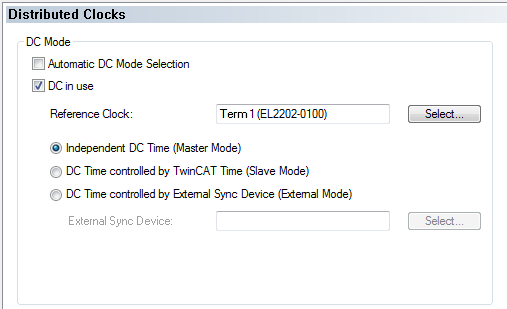

bOut := NOT bOut; - Der EtherCAT-Master des Master-Systems hat Distributed‑Clocks (DC) aktiviert. Weitere Informationen zur Einstellung finden Sie in der EtherCAT System-Dokumentation im Abschnitt Einrichtung im TwinCAT Systemmanager > Hinweise Distributed Clocks.

Eine EtherCAT-Klemme EL2202-0100 im Master-System ist DC‑Zeitgeber und gibt auch das Ausgangssignal aus.

- Größere Periodendauern, z. B. 1 s, können durch eine Zählvariable umgesetzt werden.