Features CoE

Depending on the main PDO/optional PDOs further settings can be selected in the CoE list (CAN over EtherCAT).

| Parameterization via the CoE list (CAN over EtherCAT) Please note the following general CoE notes when using/manipulating the CoE parameters:

|

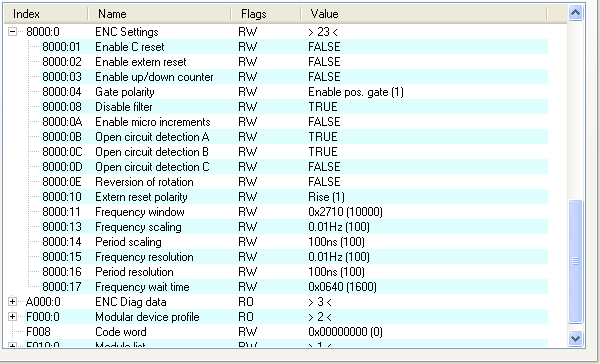

The following CoE settings from object 0x8000 are possible and shown here in their default settings, based on the EP5101-0011 as an example:

The parameters are explained in the object description chapter for the corresponding EtherCAT Box.

- Due to the different pin assignment, the following objects are not supported by the EP51x1-x002 modules!

- 0x8000:02 - Enable extern reset

- 0x8000:04 - Gate polarity

- 0x8000:10 - Extern reset polarity

- Due to different firmware, the following objects are not supported by the EP5101-2011 module!

- 0x8000:03 - Enable up/down counter

- 0x8000:08 - Disable filter

- 0x8000:0A - Enable micro increments

Additional Notes

Frequency

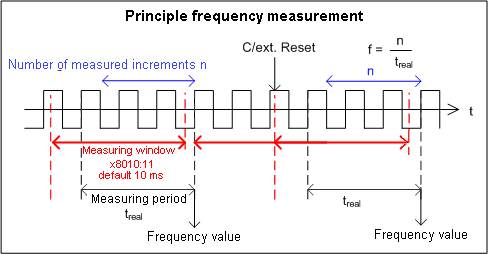

- The time window for the frequency calculation and the resolution can be parameterized in the CoE objects Frequency window 0x8000:11, Frequency scaling 0x8000:13, Frequency resolution 0x8000:15 and Frequency wait time 0x8000:17.

- The positive edges of track A are counted within the specified timeframe and the next edge including the time up to it are counted. The waiting time can be set in CoE object 0x8000:17 Frequency Wait Time (unit: ms). The default value is 1.6 sec. This is also the maximum value.

- The time window is 10 ms (default), min. 1 µs. With the default setting it is possible to measure frequencies up to approx. 800 kHz. At higher frequencies a smaller value must be selected for the timeframe.

- The time is measured with a resolution of 100 ns.

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- No frequency measurement is possible if the counter is blocked by the gate. In this case the period can be measured regardless.

- A C or external reset restarts the frequency measurement. The last frequency value remains unchanged until a new frequency value is determined.

Frequency measurement

- Basic unit 1 µs: all window sizes

Measurement sequence

- The measurement starts with a positive edge at track A. The current counter value and time (resolution: 100 ns) are stored.

- After the measuring window time has elapsed (index 0x8000:11), the system waits for the subsequent rising edge at track A, or a maximum of 1.6 seconds, or the time from Frequency Wait Time 0x8000:17.

- The frequency is calculated from the edge difference and the actual elapsed time.

Period calculation

- This calculation is carried out in the slave without reference to the distributed clocks system. It is therefore independent of the DC mode.

- During each cycle the interval between 2 positive edges of input A is counted.

- If no edge change occurs for approx. 1.6 s, any period specification is canceled.

Latch

- Activation of latch C input (Enable latch C index 0x7000:01) and saving ("latching") of the counter value

- The counter value is saved when the first external latch pulse (positive edge at input "C") is encountered after the bit has been set (TRUE) in Enable latch C index 0x7000:01 (this has priority over Enable latch extern on positive / negative edge 0x7000:02 / 0x7000:04). The subsequent pulses at the other inputs have no influence on the latch value in index 0x6000:12 if the bit is set.

- Note for Latch C valid bit: A new counter value at the latch input can only be written once the value of the Latch C valid bit (index 0x6000:01) is FALSE.

- Activation of the external latch input ("Gate/Latch") and latching of the counter value (index 0x7000:02, 0x7000:04) (not for product version x002)

- When the bit is set (TRUE) in Enable latch extern on positive edge index 0x7000:02, the counter value is saved on the latch input (index 0x6000:12) when the first external latch pulse with rising edge is encountered. The subsequent pulses have no influence on the latch value in index 0x6000:12.

- When the bit is set (TRUE) in Enable latch extern on negative edge index 0x7000:04, the counter value is saved on the latch input (index 0x6000:12) when the first external latch pulse with falling edge is encountered. The subsequent pulses have no influence on the latch value in index 0x6000:12.

- Note for Latch extern valid bit: A new counter value cannot be written to the latch input until the value of the Latch extern valid (index 0x6000:02) is FALSE.

Reset

- Counter reset via input C:

- To reset the counter, set the bit in Enable latch C index 0x8000:01.

- Resetting the counter via the external latch input (not for product version -x002)

- For a reset via the external latch input, set the bit in Enable extern reset index 0x8000:02

- Extern reset polarity index 0x8000:10 can be used to select the edge for setting the counter to zero.

• Bit not set: Counter is set to zero with falling edge.

• Bit set: Counter is set to zero with rising edge. - The functions Enable C reset (0x8000:01) and Enable extern reset (0x8000:02) cannot be enabled simultaneously.

Up/down counter

- The mode (encoder or up/down counter) can be set via Enable up/down counter index 0x8000:03. (not for product version -2011)

- Click the corresponding row of the index to be parameterized,

- enter the value "1" in the SetValue dialog and

- confirm with OK.

- Set the gate polarity accordingly via object 0x8000:04.

- An additional option for reversing the direction of rotation is to set the Reversion of rotation bit index: 0x8000:0E.

Overflow/underflow (not for product version -2011)

- Overflow/underflow control is inactive in combination with an activated reset function (C/external).

- The underflow bit (0x6000:04) is set if an underflow ...00 ->...FF occurs. It is reset if 2/3 of the counter range are underrun.

- The overflow bit (0x6000:05) is set if an overflow FF...-> 0... occurs. It is reset if 1/3 of the counter range is exceeded.

Open circuit detection

- A separate open circuit detection can be activated for each of the channels A, B, and C (index 0x80n0:0B, 0x80n0:0C, 0x80n0:0D).

- Open circuit detection is activated for channels A and B by default.

- A differential voltage of < 1.5 V (typical, subject to modification) is interpreted as an open circuit.

- If an open circuit is detected, it is indicated as process data Open circuit = TRUE (bit in object Open circuit 0x6000:07 is set). An open circuit is also indicated separately in indices 0xA000:01 (track A), 0xA000:02 (track B), and 0xA000:03 (track C).

- TxPDO state also becomes TRUE if an open circuit is detected, since invalid data have to be assumed.

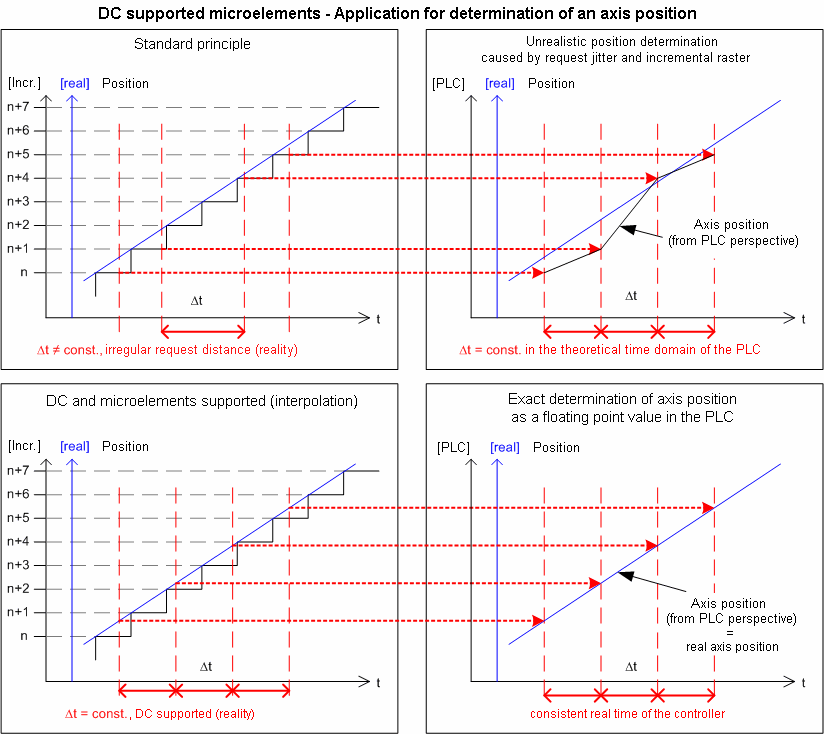

Micro-increments

- Works with and without distributed clocks, but it is only meaningful in conjunction with one of the DC modes.

- By setting the counter value only the integer component can be modified.

- The frequency measurement principle in enhanced operation mode:

The highly constant query cycles (accuracy: 100 ns) of the distributed clocks systems enable the Box to interpolate axis positions between the counted encoder increments from a certain speed. The interpolation resolution is 8 bit, corresponding to 256 values. A standard encoder with 1,024 lines with 4-way evaluation and micro-increments thus becomes a high-resolution axis encoder with 4096 x 256 = 1,048,567 lines.

If the velocity value falls below the minimum value, this is indicated by the object Extrapolation stall 0x6000:08 in the process data (not for product version -2011).