Distributed Clocks

| DC support in the EtherCAT master The distributed clock unit of the EL6695 has the DC system time, but no sync/latch unit. The corresponding initialization routine is supported by TwinCAT 3 from b4018.4, TwinCAT 2 from b2248. |

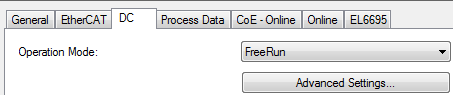

The EL6695 configuration can be viewed under the tab. For the data exchange it has the default setting “no synchronization” (“FreeRun”).

Since the EL6695 contains two complete EtherCAT slaves, the two distributed clock units are basically independent of each other. The EL6695 supports two DC synchronization mechanisms:

- Like its predecessor (EL6692) it can make the internal/external timestamp information available to the sync slave side, thereby offering the EtherCAT master stored there the option to adjust its real-time/EtherCAT cycle. Both control directions are possible.

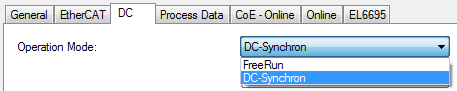

- Application under TwinCAT: Set the EL6695 to DC mode, so that TwinCAT can use it as reference clock

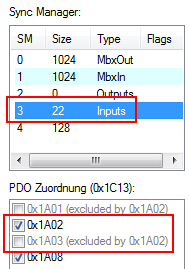

- Show and activate a timestamp PDO (0x1A02 for 64 bits or 0x1A03 for 32 bits). TwinCAT thus detects that this terminal can be used as an external reference clock and reads in the time stamps.

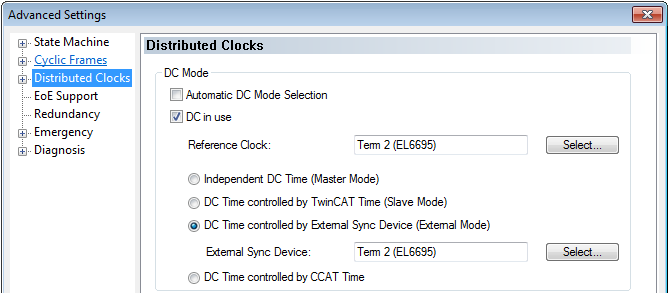

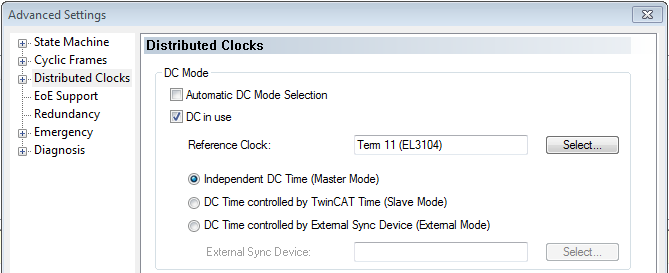

- The external reference clock can then be selected in the “EtherCAT DC master settings”:

This setting is only required on the “SyncSlave” side.

On the “SyncMaster” side an EL3104 (DC-capable) may be entered, for example:

- If the EL6695 is the first DC-capable slave in both EtherCAT systems, a direct DC coupling of the two bridge sides can be enabled without having to notify the EtherCAT masters. In this case, both EtherCAT systems/masters follow the EL6695 time, without the need for special configuration. However, a constant offset remains between the two system times.

- Both EtherCAT masters set 0x0920 DC system time offset from their side. The EL6695 accepts this and ensures frequency synchronicity for both ESC is the EL6695.

| Local control procedure not supported Unlike the EL6692, the EL6695 does not support the local control procedure “ControlValue for DC MasterClock”. EtherCAT masters should implement the timestamp procedure referred to above. |

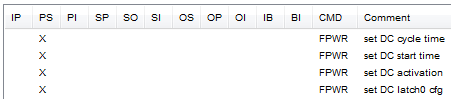

Since the EL6695 does not use the time information of the distributed clock internally but only forwards it to the other side, the use of special DC registers in the ESC is not required and not supported. In many EtherCAT devices with DC support, the master writes to DC registers 0x09A0, 0x0990, 0x0980, 0x09A8 during the status transition from PreOp to SafeOp. The EL6695 does not have these registers, which is why a write attempt during startup results in error messages from the EtherCAT master, e.g. “Init Cmd failed: set DC cycle time”.

With the EL6695, the EtherCAT master should therefore avoid writing to these registers, or it does not evaluate the WcState of the write command. In the EL6695-ESI this DC feature is identified through the flag TimeLoopControlOnly = TRUE, which the EtherCAT master can follow.