Setting the PWM clock frequency and duty cycle

The signals at outputs 3 and 4 are output with pulse width modulation, the signals being separated into duty cycle and PWM clock frequency. Separate values for duty cycle and PWM clock frequency can be defined for both outputs.

Value | Decimal | Hexadecimal |

|---|---|---|

0 % | 0 | 0x0000 |

25 % | 16383 | 0x3FFF |

50 % | 32767 | 0x7FFF |

100 % | 65.535 | 0xFFFF |

Value | Decimal | Hexadecimal | Frequency |

|---|---|---|---|

0.010 ms | 0..10 | 0x0000-0x000A | 100 kHz |

0.011 ms | 11 | 0x000B | 90.909 kHz |

0.100 ms | 100 | 0x0064 | 10 kHz |

1.000 ms | 1000 | 0x03E8 | 1 kHz |

16.38 ms | 16383 | 0x3FFF | 61.04 Hz |

65.53 ms | 65535 | 0xFFFF | 15.26 Hz |

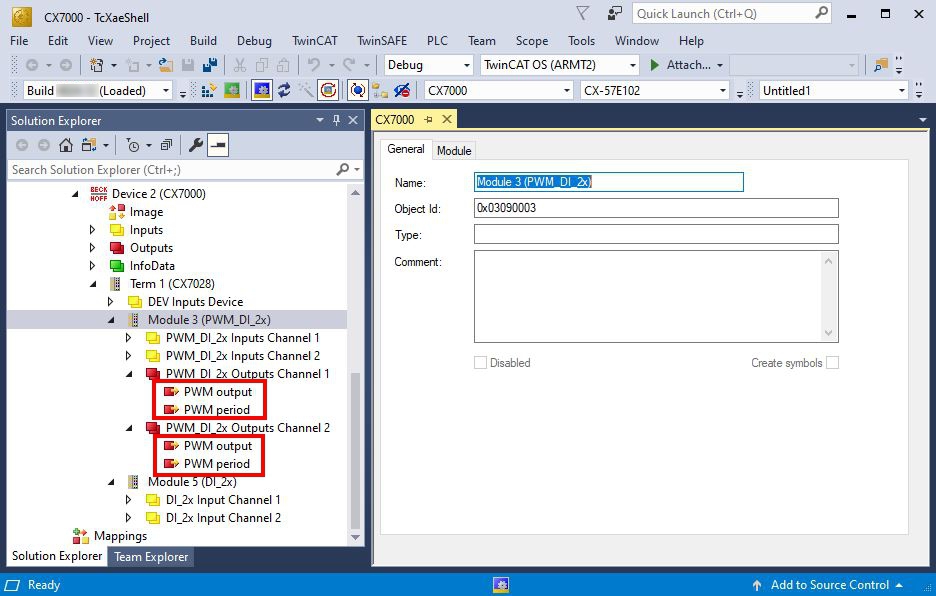

The variable PWM output correspond to the duty cycle and PWM period to the PWM clock frequency at which the signal is output.

Proceed as follows:

- 1. On the left in the structure tree, select an output for which you wish to set the duty cycle and PWM clock frequency.

- 2. Link the variables PWM output and PWM period with the appropriate variables from your PLC project.

- 3. In the variables, set the values for duty cycle and PWM clock frequency according to the above tables.