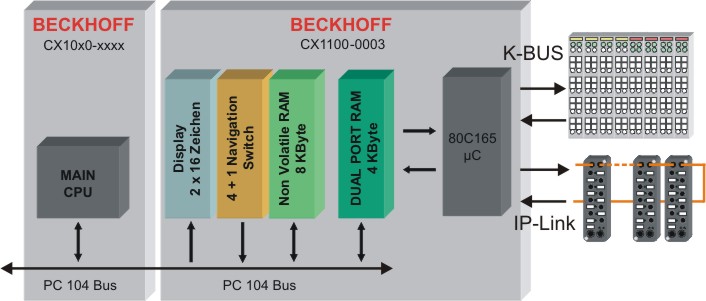

Architecture of power supply CX1100-00x3

This power supply features, except for power supply, the following functions:

- Display 2 x 16 characters

- 4+1 navigation switch

- Non Volatile RAM

- K-bus connections

- IP-Link bus connection

These functions are managed by the control program via the PC104 bus. The structure of the CX1100-00x3 is shown in the following figure:

This power supply unit features the basic functions. These functions are described in the architecture overview. Further the k-bus is supported. This interface is described in the architecture of the CX1100-0002 unit. This unit also features the access to the IP-Link bus. A fiber optics ring can be connected to the power supply The access is realized by a 4 KB dual-ported RAM. A microcontroller (80C165) manages the data transfer to the IP-Link-bus. The DPRAM is accessed by the CPU (via PC104 bus) and the microcontroller.

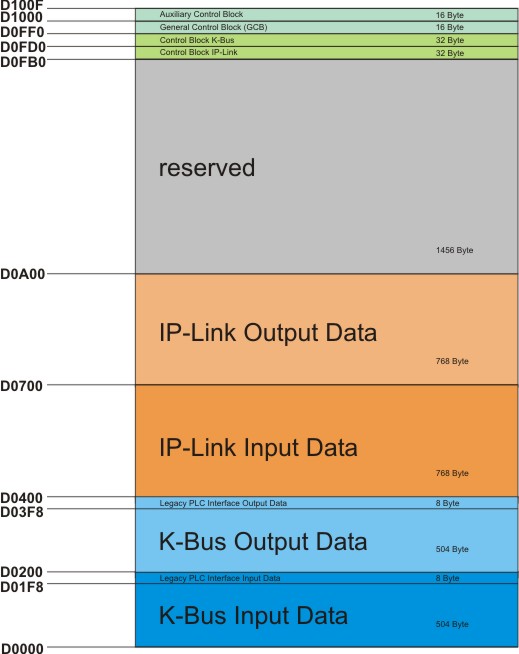

The following figure shows the memory setup of the DPRAM:

The memory image of the IP-Link bus resides in the lower memory region (D400 to D0A00). This region separates in input and output region. Since firmware version ≥ B3 it is possible to shift the I/O regions. In this way the process image can be adapted to the needed space. Each block jhas a size of 768 bytes. The following table shows the structure of the interface. The offset addresses are default values.

The IP-Link Control Block (CB IP-Link)

This section describes the layout of the control block for the IP-Link bus of CX1100-0003. This control block is located in the memory just below the I/O region of the K-bus interface.

|

CB IP-Link | ||

|---|---|---|

|

Offset |

|

Default |

|

0xFB0[2] |

IPL 2 byte plc interface to CX1100-0002/3 |

|

|

0xFB2[2] |

IPL 2 byte plc interface from CX1100-0002/3 |

|

|

0xFB4[2] |

IPL diagnosis to CX1100-0002/3 |

|

|

0xFB6[2] |

IPL diagnosis from CX1100-0002/3 |

|

|

0xFB8 |

IPL service request bitfield |

|

|

0xFB9 |

IPL service response bitfield |

|

|

0xFBA |

IPL error code |

|

|

0xFBB |

IPL error argument |

|

|

0xFBC[2] |

IPL base ptr Inputs |

0x400 |

|

0xFBE[2] |

IPL base ptr Outputs |

0x700 |

|

0xFC0-0xFC1 |

IPL cycle count |

|

|

0xFC2-0xFC3 |

IPL cycle time [µs] |

|

|

0xFC4 |

IPL bus status |

|

|

0xFC5-0xFCE |

Reserved |

|

|

0xFCF |

Retry counter |

|

IP-Link 2 byte plc interface to CX1100-0003 / IP-Link 2 byte plc interface from CX1100-0003

These two bytes for each direction - from the main CPU to CX1100 and back - special communication with the register model of the I/O microcontroller. Through this interface, a communication to K-Bus terminals can take place. The so called register model description can be found in the hardware description manuals of the terminals and bus couplers. This communication is typically used for extended diagnosis or configuration of terminals if they need to deviate from the delivery standard, e.g. changing the baud rate for RS232-terminals or gain/offset values with analog terminals.

IP-Link diagnosis to CX1100-0003 / IP-Link diagnosis from CX1100-0003

With these two bytes in each direction it is possible to retrieve diagnostic information from the attached terminals. Since the same diagnostic information is reflected in the process image input area per each terminals, there is in general no need to use this interface.

IP-Link service request bitfield / IP-Link service response bitfield

IThese two bytes contain a sequence of bits, by which certain service functions may be executed. The service function is invoked by setting the appropriate request bit, the controller executes and sets the response bit. Before the same function can be invoked again, the request bit must be set to zero and wait until the response bit is also set to zero. An execution error is signaled by raising response bit 7.

|

Bitfeld |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

|

Request |

- |

- |

- |

- |

- |

- |

Free Run |

Reset Bus |

|

Response |

Error |

- |

- |

- |

- |

- |

Free Run Active |

Reset Done |

Reset Bus:

with this bit, a reset of the K-Bus may be performed. This is necessary after the occurrence of an error (detected by examination of the "Processdata error"-byte in the GCB) e.g. after a terminal has been pulled out. After performing the K-Bus reset, the error code and error argument may be read from the locations "K-Bus error code" and "K-Bus error argument" in the CB K-Bus. If there is no error after reset, the K-Bus is ready for operation again.

Free Run:

not implemented. Reserved for future use..

IP-Link error code K-Bus error argument

If the K-Bus operation fails (bad terminal, missing end-terminal, severe EMC interference), an error flag is raised in the GCB and after a K-Bus reset, these two bytes contain the error code and error argument of the occurred fault - if it still persists.

IP-Link base ptr Inputs / K-Bus base ptr Outputs

These two byte values contain the starting offset for the K-Bus input and output process image area. In most cases the default offsets should be left unchanged. When changing one of these offsets, a "Remap" or "Reset node" in the GCB service is needed. Also care must be taken not to overlap with the IP-Link process image area, because in the CB IP-Link the offset pointers for these areas may also be changed. The Beckhoff automation software TwinCAT makes use of this base ptr feature and compacts the I/O images in the best way possible.

IP-Link cycle count

This two-byte counter is incremented with each I/O-cycle.

IP-Link cycle time

This is the time elapsed between the initiation and termination of an I/O process image update (K-Bus + IP-Link ). The time is recorded in units of microseconds and starts with writing a new cycle request to the field "PD cycle request" and it stops with the termination response in the field "PD cycle ready", in case of CX1100-0002. In case of CX1100-0003, this time reflects only the K-Bus portion of the total I/O time.

IP-Link bus status

This byte value can take only two states:

- Byte = 0 → K-bus is ok

- Byte ≠ 0 → K-bus fault

This information is also reflected in the "Processdata error" field (bit0) of the GCB.

Retry counter

This is a retry counter which is incremented each time the microcontroller needs to redo a cycle because of a communication error. This counter can be used for judgment of the K-Bus signal quality.