Restrictions for Clock Frequency

Firmware ≥ v2.10 build 0015 allows setting different frequency values.

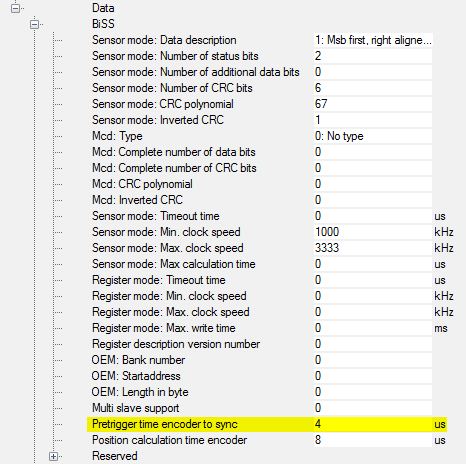

| Possible values of the clock frequency to be set: 2000, 2500, 3333, 5000 [kHz]. The clock frequency can be changed in the parameter P-0-0150 under: Parameter channel → Data → BISS → Sensor mode: Max. clock speed |

If other values are set, the software will use the next possible lower value. Lower clock frequency causes longer data transmission time.

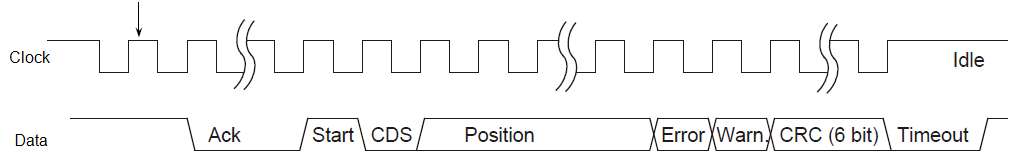

Communication signals between AX5000 and encoder look like this:

During the "Ack" period the encoder prepares for transferring the actual position value. With the rising edge at "Start" it signals to be ready and then starts transferring data.

Due to its internal cycles the AX5000 needs the position at certain point of time after it has started reading. This means the time from the first rising edge of the clock signal to the last CRC bit must not exceed 18µs.

Example:

Clock frequency: 3.333 MHz => Bit time = 1/ 3.333MHz = 0.3 µs

Number of bits to be transferred for a position telegram:

Example 1 | Example 2 |

|

|---|---|---|

4 µs | 8 µs | Preparing time of encoder ("Ack") |

Number of bits |

| |

1 | 1 | Start |

1 | 1 | CDS (Cyclic data slave, not used, always 0) |

26 | 32 | Position |

1 | 1 | Error (status) |

1 | 1 | Warning (status) |

6 | 6 | CRC |

1 | 1 | Stop/ Timeout |

37 | 43 | Number of clock cycles for complete telegram |

Example 1 | Example 2 |

|---|---|

Transmission time = 4 µs + 37 x 0.3 µs = 15.1 µs < 18 µs | Transmission time = 8 µs + 43 x 0.3 µs = 20.9 µs > 18 µs |

|

20.9 µs - 18 µs = 2.9 µs

|

|

|

| The value for the pretrigger must not exceed 15 µs! |