Beispielschaltungen für SW-seitig einstellbare Widerstande

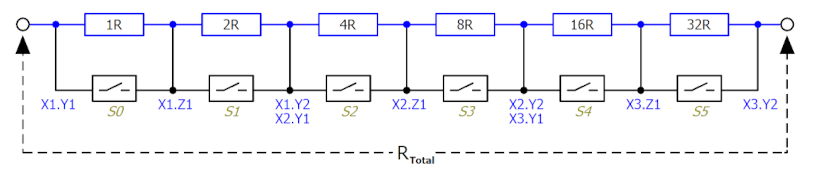

Eine erste „übliche“ und relativ einfache Schaltung ist mit in Reihe geschalteten binär gestuften Widerständen realisierbar, die jeweils mit einem Schalter gebrückt werden können: hierbei wird mit einem Schalterpaar vom gemeinsamen Knotenpunkt ein Widerstand linkseitig und einer rechtsseitig gebrückt. Es bleiben von einem Schalterblock je zwei Schalter unbenutzt, da von jedem Schalterblock (1:4 Multiplexer-Gruppe) nur zwei verwendet werden. Eine 6-Bit-Umsetzung wäre als 1. Beispiel:

Abb.10: Beispiel 1: In Reihe geschaltete binär gestufte Widerstände

Abb.10: Beispiel 1: In Reihe geschaltete binär gestufte WiderständeMit der Schalter-Konfiguration S=#010010 würde sich für R = 1 Ω beispielsweise ein Widerstandswert von 45 Ω ergeben, wenn:

RTotal = (S0neg ∙ 1 Ω + S1neg ∙ 2 Ω + S2neg ∙ 4 Ω + S3neg ∙ 8 Ω + S4neg ∙ 16 Ω + S5neg ∙ 32 Ω),

wobei S5 als MSB gelte. Da eine 1 = “Schalter geschlossen“ einen Widerstandswert eliminiert und entsprechend mit einem Wert 0 addiert, sind die Indizes „neg“ bei S für „Wert-negiert“ angegeben.

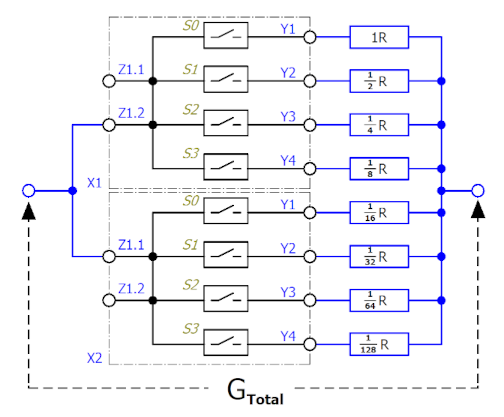

Bei einem 2. Beispiel werden alle Schalter eines Schalterblocks verwendet. Die Widerstände sind parallel zueinander an- und abschaltbar:

Abb.11: Beispiel 2: Parallel geschaltete binär gestufte Widerstände

Abb.11: Beispiel 2: Parallel geschaltete binär gestufte WiderständeHierbei kann die Berechnung des Gesamtwiderstandes mit Hilfe des Leitwertes etwas vereinfacht werden: das MSB S7 schaltet für 1 = “Schalter geschlossen“ den höchsten Leitwert 128 S hinzu, eine Negation liegt nicht vor. In der Gesamtbetrachtung verhält es sich wie bei einer Reihenschaltung:

GTotal = (S0 ∙ 1 S + S1 ∙ 2 S + S2 ∙ 4 S + S3 ∙ 8 S + S4 ∙ 16 S + S5 ∙ 32 S + S6 ∙ 64 S + S7 ∙ 128 S)

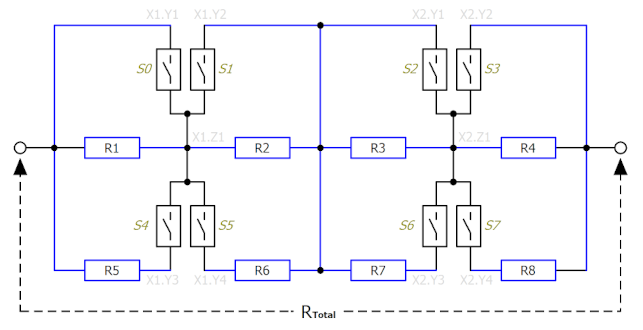

Wie durch die Kehrwertbildung für RTotal = (GTotal)-1 ersichtlich liegt hier im Gegensatz zur Reihenschaltung aus dem ersten Beispiel eine Hyperbelverlauf vor. In der Reihenschaltung aus Beispiel 1 hingegen gibt es für jeden Schalterwert zum Widerstandswert einen linearen Zusammenhang. Eine Kombination von Reihen- und Parallelschaltung im 3. Beispiel kann den Hyperbelverlauf in einem linearen Verlauf überführen:

Abb.12: Beispiel 3: In Reihe und parallel geschaltete binär gestufte Widerstände

Abb.12: Beispiel 3: In Reihe und parallel geschaltete binär gestufte WiderständeEs ist ersichtlich, dass hier wiederum redundante Schalterstellungskombinationen vorliegen, da beispielsweise S4 keine Auswirkung hat, wenn S0 geschlossen ist usw. Dafür liefert diese Schaltung zumindest für (ideale) binär gestufte Widerstandswerte einen linearen Verlauf. Vorgesehen ist, dass die Widerstände R5 bis R8 in Folge die gleichen Werte haben wie R1 bis R4 in Folge. Z.B. bei Festlegung der Werte:

R1 = R5 = 2 Ω, R2 = R6 = 4 Ω, R3 = R7 = 8 Ω und R4 = R8 = 16 Ω

können Widerstände von 0…30 Ω in ein-Ohm-Schritten geschaltet werden.

Es liegt nahe, für jegliche derartige Schaltungen alle unterschiedlichen Gesamtwiderstandswerte für jede Schalterkombination mittels Programmskript zu ermitteln. Hierfür sei an dieser Stelle vorab ein praktikabler Ansatz für Beispiel 3 in ST (TwinCAT 3.1) gegeben:

ausgehend von einer Funktion zur Berechnung zweier parallel geschalteter Widerstände:

FUNCTION F_RG_PAR : LREAL

VAR_INPUT

nR1, nR2 : LREAL;

END_VAR// total resistance calculation of two parallel resistors

// special cases, if one resistor is zero the other will be returned

F_RG_PAR := SEL((nR1=0), SEL((nR2=0), ((nR1 * nR2)/(nR1 + nR2)), nR1), nR2);und einer weiteren Funktion zur Berechnung des Gesamtwiderstandes:

FUNCTION F_RG_R_SIMU : LREAL

VAR_INPUT

paR : POINTER TO ARRAY[1..16] OF LREAL;

nS : UINT;

END_VAR

VAR

nI : BYTE;

END_VAR// total resistance calculation by nS: S0=bit0, S15=bit15

// (for 2 x 8 resistances using S8..S11 for S4..S7)

F_RG_R_SIMU := 0;

FOR nI := 0 TO 7 DO

F_RG_R_SIMU := F_RG_R_SIMU

+ SEL(((SHR(nS, nI) AND 1) = 1), F_RG_PAR(paR^[nI+1],

SEL(((SHR(nS, (nI+8)) AND 1) = 1), 0, paR^[nI+9])), 0);

END_FORkönnen mit folgendem Code alle Gesamtwiderstandswerte bei gegebenen Widerständen aus der Schaltung in Beispiel 3 berechnet werden:

PROGRAM MAIN

VAR CONSTANT

n8Bit : UDINT := 255;

//n16Bit : UDINT := 65535;

END_VAR

VAR

bStart : BOOL := FALSE;

bUse_E96 : BOOL := FALSE;

// Array with resistor values 2 x 2, 2 x 4 and 2 x 8 circuit

aR_List_bin : ARRAY[1..16] OF LREAL := [

2, 4, 8, 16, 32, 64, 128, 256,

2 ,4 ,8 ,16 ,32 ,64 ,128 ,256

];// Ideal/theoretical values

aR_List_E96 : ARRAY[1..16] OF LREAL :=[

2, 4.02, 8.06, 16.16, 32.39, 63.4, 130.19, 261.02,

2, 4.02, 8.06, 16.16, 32.39, 63.4, 130.19, 261.02

];

aS_List : ARRAY[0..n8Bit] OF UINT; // array size with max number of switch combinations for 2 x 4 circuit

rValue : ARRAY[0..n8Bit] OF LREAL; // array size with max number of total resistor values for 2 x 4 circuit

nI, nJ, nMaxComb : UDINT;

nState : BYTE := 0;

END_VAR// execution part

CASE nState OF

0:

// create switch combinations:

// 1 = switch closed

IF bStart THEN

bStart := FALSE;

// use switches for circuit with 8 resistors

// S0..S3 and S8..S11

FOR nJ := 0 TO 15 DO

FOR nI := 0 TO 15 DO

aS_List[nI+16*nJ] := UDINT_TO_WORD(16#F0 OR (nI OR SHL(nJ, 8)));

// - unused switch combinations 0xXXF0, (S4..S7) must be closed

//(S12..S15 don't care)

END_FOR

END_FOR

// (for loops should be nState numbers when task cycle time not enough)

nMaxComb := n8Bit;

nI := 0;

nState := nState + 10;

END_IF

10:

// calculate total resistor values:

IF bUse_E96 THEN

rValue[nI] := F_RG_R_SIMU(ADR(aR_List_E96), aS_List[nI]);

ELSE

rValue[nI] := F_RG_R_SIMU(ADR(aR_List_bin), aS_List[nI]);

END_IF

IF(nI = nMaxComb) THEN

nState := 0;

END_IF

nI := nI + 1;

END_CASEHinweis: bei Einsatz dieser Schaltungen ist für den Gesamtwiderstand u.a. in den technischen Daten der für die verwendete Klemme angegebene Einschaltwiderstand jeweils zu berücksichtigen!

Download tpzip-Datei.