Impedanz und Routing

Die folgenden Punkte sind für in der Design Phase des PCB zu beachten:

- Die E-Bus-Leiterbahnen sind in den inneren Ebenen zu routen.

- Die differentielle Impedanz der LVDS Leiterbahnen muss 100 Ω betragen.

- Breite und Abstand des Differenzsignals sind abhängig vom konkreten Aufbau der Leiterplattenebenen und sind einzeln zu berechnen.

- Die Differentialsignale sollten nebeneinander (edge coupled) geroutet werden.

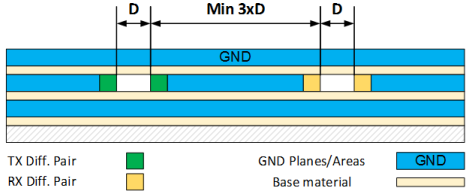

- Der Abstand zwischen den Differentialpaaren sollte dreimal größer als der innere Abstand (s. folgende Abb. (D)) sein.

- Zwischen den differentiellen Leitungen (D) darf sich keine GND-Fläche ausbilden. Dies ergibt sich üblicherweise aufgrund der geforderten Impedanz.

- Differentialpaare sollten ohne VIAs (vertical interconnect access) geroutet werden, um Impedanzsprünge zu vermeiden.

- Maximalwerte für nicht gekoppelte Leiterbahnen und Gesamtlängen der Leiterbahnen finden Sie in der Spezifikation für LVDS - Signale ANSI/TIA/EIA-644 "Electrical Characteristics of Low Voltage Differential Signaling (LVDS)"

Hinweis | |

Kurzschlüsse vermeiden Bei der Querschnittskonfiguration ist auf Kurzschlüsse zu achten! |