Distributed Clocks (DC)

The Embedded PC CX8110 supports distributed clocks (DC). This enables the CX8110 to synchronize with a higher-level controller.

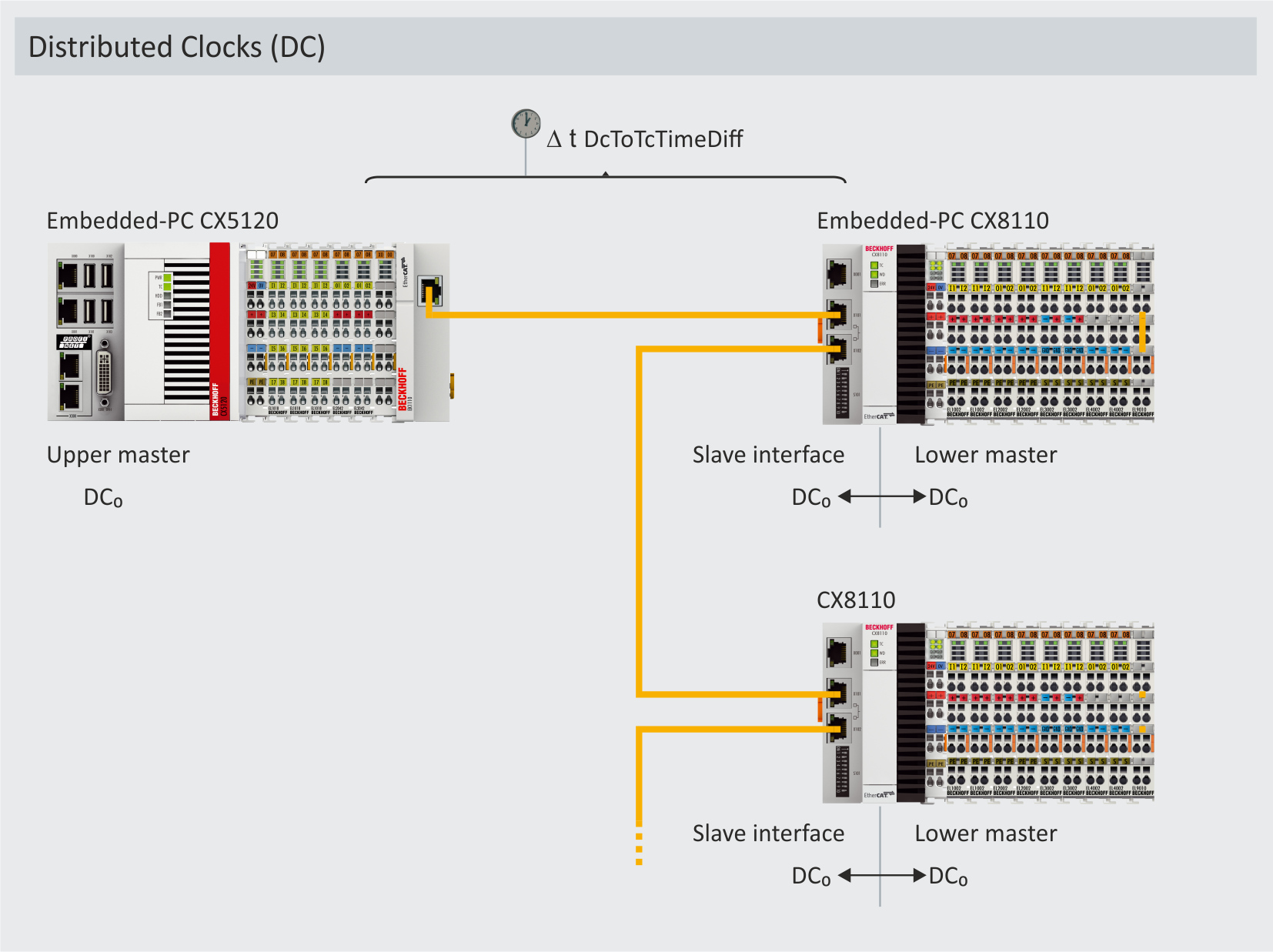

Synchronization is best illustrated by two clocks, a master clock and a slave clock. The CX8110 is the slave clock and must follow the master clock. The two clocks do not have to have the same absolute time. Rather, the time difference (DcToTcTimeDiff) to the master clock becomes a constant after synchronization. It does not matter when a time stamp is created in the CX8110. The time stamp always has the same time difference to the master clock, even after years have passed.

If the EtherCAT connection is interrupted or the higher-level control (master clock) is switched off and switched on again after some time, the time difference between master clock and slave clock must be redefined. From this point on, a new time difference applies that differs from the previous value.

For optimum DC control, select a sync task less than or equal to 5 ms. The smaller the sync task, the better the DC control. Make sure the CPU load is below 60%.

Restrictions for K-bus terminals

The distributed clocks function (DC) usually only makes sense if the CX8110 Embedded PC is used with E-bus terminals on the right-hand side and therefore EtherCAT. If you only use K-bus terminals, the distributed clocks function (DC) is rather meaningless. The following sections therefore focus on the use of distributed clocks (DC) in conjunction with a lower-level EtherCAT master.